Description

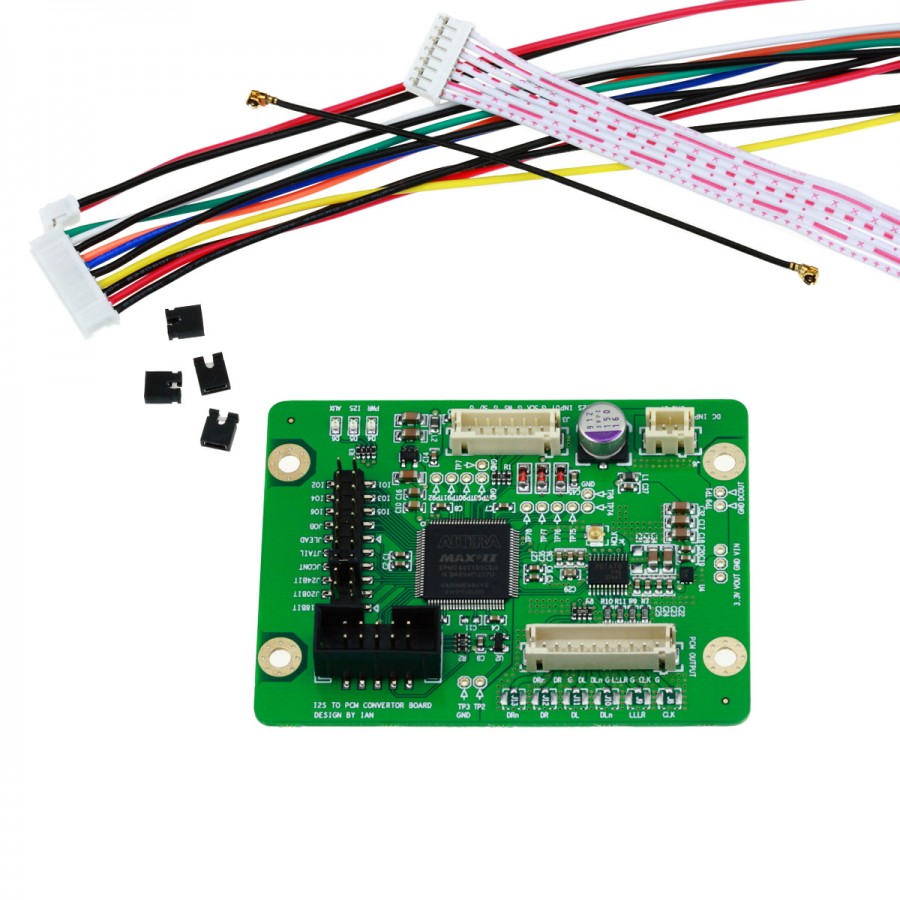

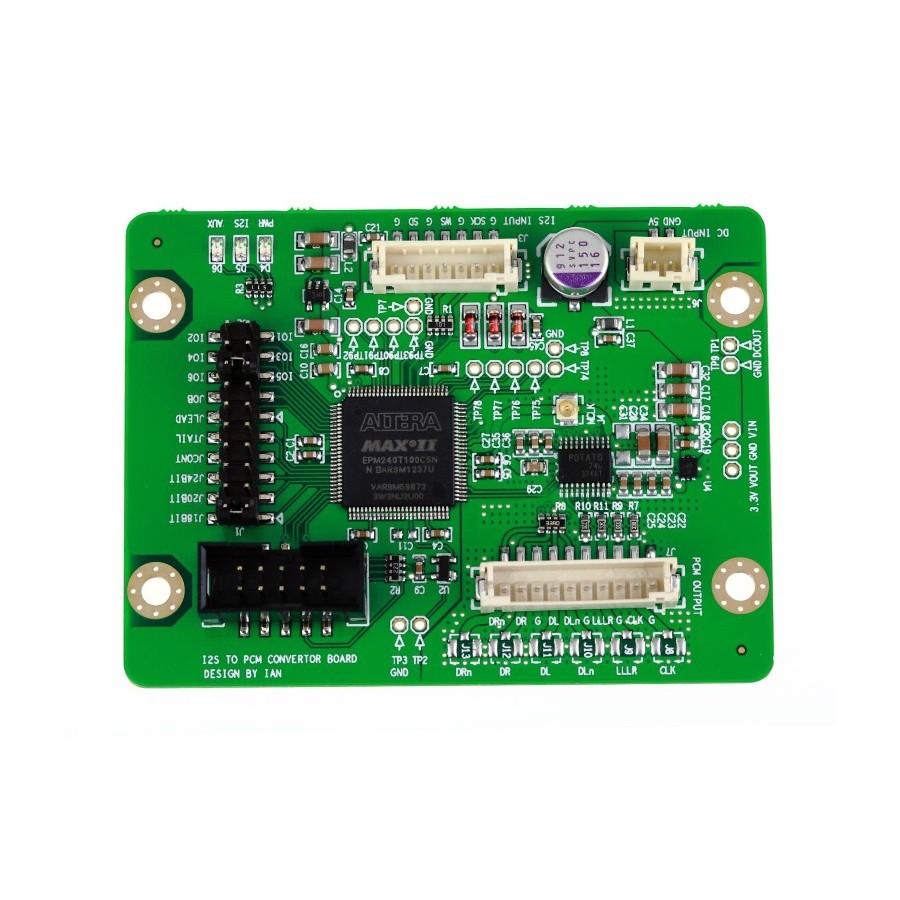

Ian Canada

Module de Conversion I2S vers PCM

De nombreuses personnes apprécient le son des convertisseurs numérique/analogique MULTIBIT traditionnels, tels que les AD1865/62, PCM170402, PCM63, TDA1541/A et bien d’autres. Cependant, la plupart de ces DAC MULTIBIT ont été conçus pour fonctionner avec des puces de filtrage numérique à travers une interface PCM qui transmet les données gauche et droite simultanément. Dans ce cas, le problème est que la qualité sonore et la fréquences d’échantillonnage (Fs) maximum de ces DAC peuvent être limitées par les performances de la puce de filtrage numérique d’oversampling, à cause d’une faible précision de calcul, de l’algorithme d’interpolation et d’anciennes technologies délivrant un niveau de jitter élevé.

Pour améliorer la qualité sonore en utilisant une meilleure technologie de réduction du jitter et permettre la lecture de taux d’échantillonnages plus élevés, il est nécessaire de se débarrasser de la limitation de la puce de filtrage numérique en pilotant le DAC MULTIBIT depuis un filtre d’oversampling haute performance ou en diffusant directement un flux audio à fréquence d’échantillonnage élevée. Il est ainsi nécessaire d’utiliser un système à jitter optimisé pour contrôler le DAC MULTIBIT en mode NOS depuis un bus I2S.

Ce module I2S vers PCM de chez Ian Canada a été développé exactement dans cette optique afin d’améliorer les performances sonores de ces systèmes audio.

Points clés :

- Supporte les sorties PCM 16/18/20/24bit.

- Accepte les signaux d’entrée I2S de 16 à 32bit avec SCK de 32*Fs à 64*Fs.

- Mode NOS pur avec conversion de format bit-perfect.

- Design haute vitesse avec support de taux d’échantillonnages jusqu’à 384kHz (Fs) et un MCLK maximum de 100MHz.

- Supporte les DAC MULTIBIT PCM63, AD1865, AD1862, PCM1704, PCM1702, TDA1541/A et bien d’autres.

- Supporte le fonctionnement du TDA1541/A en mode binaire décalé.

- Mode pleine vitesse et mi-vitesse sélectionnable via jumper.

- Synchronisation L/R simultanée, lancement de la conversion numérique/analogique sur le même front de verrouillage pour éliminer la différence de phase L/R.

- Afin de réduire le bruit de fond du DAC l’horloge peut être arrêtée après le décalage des données dans le DAC (par défaut).

- Supporte les configurations DAC double mono.

- Architecture logique de synchronisation optimisée pour le jitter.

Caractéristiques

| Entrées | Connecteur PCB |

| Sorties | Connecteur PCB |

| Taux d’échantillonnage max | 384kHz |

| Puce interface | NC |

Téléchargement

Notice (EN)

Téléchargement (965.15k)

Reviews

There are no reviews yet.